HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

June 2020, HDL Works announces the release and immediate

availability of

EASE 9.2, the Graphical HDL Design tool.

EASE is the most intuitive Graphical HDL Design Entry tool in the industry. Providing the user with a better means of communication, documentation, design entry and modification for any HDL design targeted for FPGA or ASIC. With its four integrated editors (block diagram, state diagram, truth table and text editors) EASE offers a suitable design entry for every HDL requirement. It includes integration with the industry standard revision control system Subversion for real multi-user support.

In EASE 9.2 we have made a start with supporting SystemVerilog. This release focusses around the synthesis functionality of the language. The internal SystemVerilog parser is fully compliant and can be set in 2005 and 2009 mode. Verilog (all versions) are a part of the SystemVerilog language. There are some properties that apply to both Verilog and SystemVerilog. The default language can be set to SystemVerilog in the project properties dialog. SystemVerilog items for which EASE has a graphical representation in the database view are:

Packages and programs have text contents. User defined types can be declared in packages and used in interfaces, modules and programs. The type definition of nets and ports in those units is improved and the use of memory signals with a range and a dimension: like [7:0]example[31:0]is now supported.

Packages can be used inside a module or interface using an import statement. The import statement is either placed before or inside the module or interface.

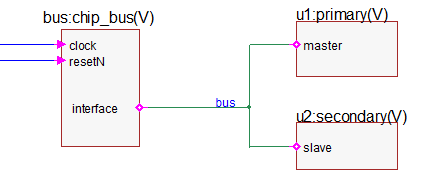

An ‘interface’ is a new SystemVerilog construct to encapsulate the communication information between Verilog modules. The contents of an interface can be a block diagram or a text file. A number of ‘modports’ can be defined on an interface. These ‘modports’ are used on other modules. An interface is instantiated like a module, but it has one special port named ‘interface’, which is always present on the instantiated interface. The interface port is used to connect to other ‘modports’ on instantiated modules. Ease supports the use of both named ‘modports’ and generic ‘interface ports’.

The HDL file parts for text architectures, packages, processes and concurrent

statement blocks are now located inside a folder named ‘ease.hdl’ (inside the

<project>.ews)

So a process file snippet is now in:

<ease.hdl>/<library/<entity>/<architecture>/process.vhdNew text files (including Verilog include files and other internal HDL files) will now be placed inside

<project>.ews/ease.hdl/folder. This reduces the amount of folders present in the <project>‘.ews’ folder.

EASE can use a number of configuration files, which can reside in the user or corporate location. To simplify the use of these configuration files and show which files are present a new ‘User and corporate configuration files dialog’ is used. The dialog allows you to setup (create/edit/delete) configuration files for which no user interface is present. New files are created using a template from the installation showing you the required format.

A number of new lint checks have been added to EASE:

EASE 9.2 is available now. Prices begin at € 4800 for a perpetual license. EASE can be downloaded and evaluated freely from the HDL Works website.

HDL Works develops and markets high-performance, intuitive tools for complex HDL design across a wide spectrum of applications. Its software products are available for Linux and Windows platforms. HDL Works currently holds ConnTrace, EASE, HDL Companion, IO Checker and Scriptum in its product portfolio. Headquartered in Ede, The Netherlands, HDL Works is privately held.

HDL Works BV

###

ConnTrace, EASE, HDL Companion, IO Checker and Scriptum are trademarks of HDL

Works.

Copyright © 2004 - 2026 HDL Works