HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

November 2025, HDL Works announces the release and immediate availability of

EASE 9.6, the Graphical HDL Design tool.

EASE is the most intuitive Graphical HDL Design Entry tool in the industry. Providing the user with a better means of communication, documentation, design entry and modification for any HDL design targeted for FPGA or ASIC. With its four integrated editors (block diagram, state diagram, truth table and text editors) EASE offers a suitable design entry for every HDL requirement. It includes integration with the industry standard revision control system Subversion for real multi-user support.

When you have many ports on entities the diagrams get more difficult to read due to the many signals crossing. The use of ‘Meta’ ports and nets is a solution to this problem. A ‘Meta’ port represents a number of ports on a block or on the diagram. Likewise a ‘Meta’ net represents a number of signals in a diagram.

A meta port is created by merging 1 or more component or diagram ports into a meta port using the context menu of a port.

A meta net is created merging multiple nets in to a meta net or by starting a wiring action at a meta port.

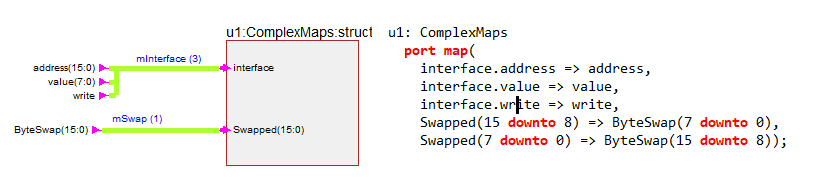

Besides reducing the visible diagram complexity the new Meta port and net functionality offers the possibility of complex port maps in which you can:

• concatenate signals

• associate individual record and array elements

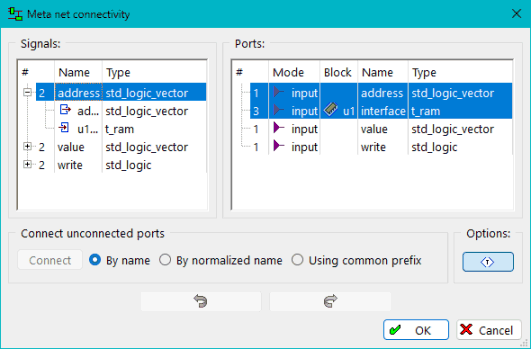

A meta port can only be connected to a meta net. A meta net can be connected to both meta ports and ‘normal’ ports. When multiple signals are connected to a single port connection properties must be defined to create the intended portmap. How the signals inside a meta net connect to the ports is controlled in the meta connections properties dialog. The dialog offers additional functionality besides connecting port items to signals through its context menus. Different context menus are available in the Signals and Ports windows. They allow you to:

The VHDL-2019 standard allows you to define a ‘view’ on a record type. A view assigns a direction to each signal in the record. The view definition can then be used as mode indicator on an entity port.

Below is an example for a simple memory interface with 5 signals. The record and its views have been defined in a package.

type t_ram is record

address : STD_LOGIC_VECTOR(15 downto 0);

enable : STD_LOGIC;

toStore : STD_LOGIC_VECTOR(7 downto 0);

value : STD_LOGIC_VECTOR(7 downto 0);

write : STD_LOGIC;

end record; -- t_ram

view vRamIn of t_ram is

toStore : in;

value : out;

address : in;

enable : in;

write : in;

end view vRamIn;

alias vRamOut is vRamIn'converse;

A second advantage is that the use of views reduces the size of the instance port map. An additional advantage is that when the interface between the entities needs to be adjusted this can done by just changing the type and view definitions.

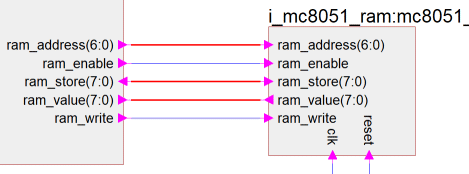

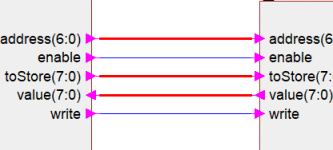

The diagram image on above shows the regular signal interconnect, while the diagram below uses a record view to reduce the amount of visible interconnect.

The only disadvantage of using views is that views are not yet supported by all EDA tool vendors.

In the User preference dialog, Application page, you can select both a fixed-pitch font and a proportional font (type face and font size) which are used where applicable.

The TIFF image file format is no longer supported (image on diagram, export image to file).

EASE 9.5 is available now. Prices begin at € 5450 for a perpetual license. EASE can be downloaded and evaluated freely from the HDL Works website.

HDL Works develops and markets high-performance, intuitive tools for complex HDL design across a wide spectrum of applications. Its software products are available for Linux and Windows platforms. HDL Works currently holds BoardTrace, EASE, HDL Companion, IO Checker and Scriptum in its product portfolio. Headquartered in Ede, The Netherlands, HDL Works is privately held.

HDL Works BV

###

ConnTrace, EASE, HDL Companion, IO Checker and Scriptum are trademarks of HDL

Works.

Copyright © 2004 - 2026 HDL Works