HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

November 2022, HDL Works announces the release and immediate availability of IO

Checker 5.0,

the FPGA and PCB IO verification tool.

IO Checker will verify that signal names used in the FPGA are connected to the appropriate signals on the PCB. Additionally it verifies the voltage values connected to the FPGA power and reference pins. IO Checker uses rules (based on regular expressions) to match the signals names in both the FPGA and PCB design environment. The rules can be generated automatically and be fine-tuned by the designer. The automated approach will often match 80% to 90% of all device pins.

The flexibility of IO Checker allows it to be used in any design flow and does not require any design methodology. The rules generator in combination with the sorted problem view allows engineers to validate a 1000+ pin device in half an hour.

Buttons with images and other graphical user interface elements will follow the scale size set in Windows and Linux.

In the User preference dialog, Application page, you can specify a font size increase, which will increase all font sizes for application text, for which you cannot select the font and size in the preference options (like in menus, dialogs and tab labels).

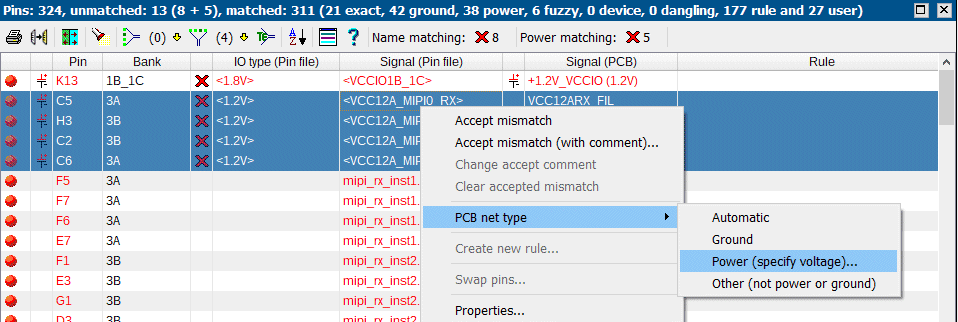

The context menu of the pin view has been simplified. The ‘Accept name mismatch’ and ‘Accept power mismatch’ entries have been merged in ‘Accept mismatch’. The item 'Change accept comment' has been added to change comment on a user accepted mismatch.

The items ‘Set/unset PCB net as a ground net…’, ‘Specify PCB voltage…’ and ‘Clear PCB voltage’ are moved in to the sub-menu ‘PCB net type’. Automatic is the default and should be used to remove the ground net of PCB voltage setting. Use ‘Other’ to force a net which was recognized as either ground or power net to be a regular user IO net.

The netlist type of a net can be set on any net. In the past power a voltage value could only be set on a net connected to a FPGA power pin. If a PCB net is manually marked as being a ground net we will now show this in the pin view by adding ' (-> GND)' to the name.

A new dialog to quickly edit groups of signals in the Signal view using regular expressions has been added for the signal view. This function is useful to change signals imported from the PCB with pre- of suffixes which need to be removed or changed.

Select the signals you want to change in the Signal view and choose 'Rename signals...' from the context menu.

The device view now shows pin labels for QFP packages.

Pins which are reserved, but different than do-not-use (like RSVDGND from Xilinx) show an R symbol.

Pins which can be both configuration and user IO have a diamond symbol inside the boundary.

The following changes have been made in the FPGA - PCB verification:

The ‘Accept power mismatch’ and ‘Accept name mismatch’ functionalities have been merged into a single ‘Accept mismatch’ function.

FPGA Control pin verification:

FPGA ground pin verification:

FPGA power pin verification:

The above options can be set (independently) in the Pin view matching and project verify options, and verify wizard dialog.

The ‘Clear unused PCB net types‘ is only enabled when it can be set and is used to removed voltage and ground settings on nets which are no longer present in the netlist.

Fabrication netlist format IPC-D-356 (often present with the Gerber data) has been added. The netlist type of a net (power, ground, normal) can be set on any net. In the past power (with a voltage value) could only be set on a net connected to a FPGA power pin.

If a PCB net is manually marked as being a ground net we will now show this in the pin view by adding ' (-> GND)' to the name.

Added the bank number to the tables ‘Pin list by severity’ and ‘List by FPGA pin’. Replaced fixed font sizes by ‘em’ and improved header. Replaced named anchors by ‘id’ attributes.

The dialog to wire non-FPGA symbols in Cadence Allegro (Tcl command Ioc::SchematicCsvDlg) has been extended with a ‘Column for the port’ entry. It allows you to use a specific port for a signal. When it is set the ‘Ports options’ entry is ignored. The ports used need to be present in the Allegro SKILL configuration file.

IO Checker 5.0 is available now. Prices begin at € 750 or US$ 790. IO Checker can be downloaded and evaluated from the HDL Works website.

HDL Works develops and markets high-performance, intuitive tools for complex HDL design across a wide spectrum of applications. HDL Works currently holds BoardTrace, EASE, HDL Companion and IO Checker in its product portfolio. Headquartered in Ede, The Netherlands, HDL Works is privately held.

HDL Works BV

###

BoardTrace, EASE, HDL Companion, IO Checker and Scriptum are trademarks of HDL

Works.

Copyright © 2004 - 2026 HDL Works