HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

February 2024, HDL Works announces the release and immediate availability of IO

Checker 5.1,

the FPGA and PCB IO verification tool.

IO Checker will verify that signal names used in the FPGA are connected to the appropriate signals on the PCB. Additionally it verifies the voltage values connected to the FPGA power and reference pins. IO Checker uses rules (based on regular expressions) to match the signals names in both the FPGA and PCB design environment. The rules can be generated automatically and be fine-tuned by the designer. The automated approach will often match 80% to 90% of all device pins.

The flexibility of IO Checker allows it to be used in any design flow and does not require any design methodology. The rules generator in combination with the sorted problem view allows engineers to validate a 1000+ pin device in half an hour.

Menu changes

The ‘Edit’ menu in the main menu bar changed into ‘Project‘. Menu items from the ‘Tools’ menu that change the project have been moved to the ‘Project’ menu.

Row filters in various views

The Pin view row filter and device view pin filter have been reorganized and have three distinct groups.

All filters now have an ‘OK’ and ‘Cancel’ button at the bottom. Clicking outside of the filter will now cancel any changes you made after opening the filter.

At the right of each filter button there is a

‘Clear filter’ button to remove all filters.

A new functional group name ‘IO’ has been added and all pins of a device are now placed in one or more functional groups. Pins can belong to multiple groups. (Like Intel MAX10 JTAG or VREF pins, which can also be used a regular user IO.)

Changed visualization of control, JTAG and VREF pins in device view:

The device view legend dialog is now modeless.

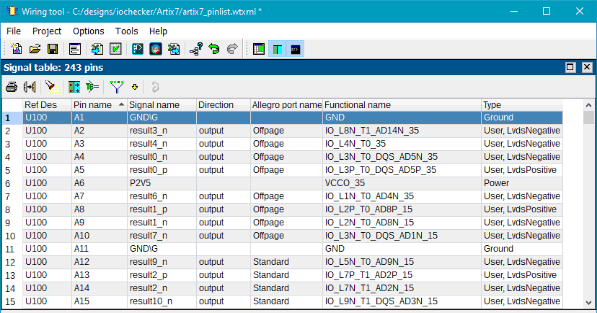

A new wiring utility has been created to wire symbols in Cadence Allegro / SystemCapture and Altium Designer.

It is started from the 'Tools >> Wiring' tool menu.

The main advantages of the new wiring tool:

This first release can wire symbols in Cadence Allegro / SystemCapture and Altium Designer.

Support for compressed Cadence packager pstcmdb.dat files. Support for the Allegro System Capture compressed ‘pstedb.cdsz’ format.

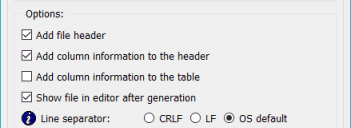

The CSV Pin data and Signal data export dialogs received additional options on what kind of file header should be created. The Line separator option allows to to specify the line style ending.

IO Checker 5.1 is available now. Prices begin at € 800 or US$ 870.

IO Checker can be downloaded and evaluated from the HDL Works website.

HDL Works develops and markets high-performance, intuitive tools for complex HDL design across a wide spectrum of applications. HDL Works currently holds BoardTrace, EASE, HDL Companion and IO Checker in its product portfolio. Headquartered in Ede, The Netherlands, HDL Works is privately held.

HDL Works BV

###

BoardTrace, EASE, HDL Companion, IO Checker and Scriptum are trademarks of HDL

Works.

Copyright © 2004 - 2026 HDL Works