HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

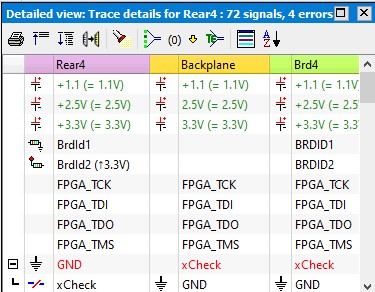

When a net has been identified as power net the recognized voltage is shown between parenthesis after the signal name and a power icon is displayed in the circuit type column. Ground nets get an ground icon.

Other issues in the interconnect verification are pull-up / pull-down circuits and IO standards which complicate verification. You want to make sure that there is only one pull-down (or pull-up) resistor on a signal line when a board is placed in the system.

BoardTrace analyzes the netlist and determines the power / ground signals and locates the pull-up and pull-down resistors. The resistors are shown in the netlist trace. The pull-up voltage (when determined) is shown between parenthesis.

Some IO standards require the use of a series resistor in the signal line. Often one of the nets at the 2 sides of the resistor receives an internal (system generated) net name. Like $1N2129, while the other side has a logical name like MainClk1_p. In this case BoardTrace will use the logical (meaningful) name instead of the internal name.

In the trace view this is shown as: $1N2129 (→MainClk1_p)

Copyright © 2004 - 2026 HDL Works